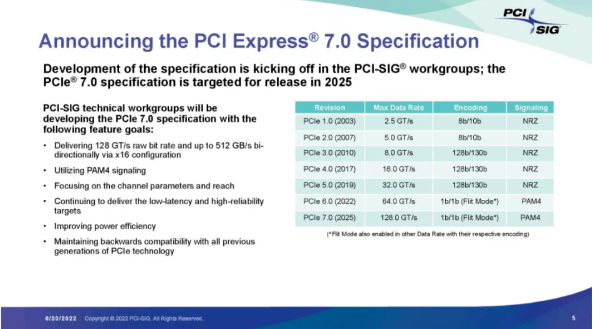

2022年PCI-SIG開發者大會正在如火如荼舉行,而藏在無處不在的PCIe接口標準背后的標準委員會PCI-SIG宣布,PCIe7.0規范的目標是在2025年向其成員發布,數據速率高達128GT/s。在編碼開銷之前,這相當于通過16通道(x16)連接實現512GB/s的雙向吞吐量。PCI-SIG是PCIe接口背后的聯盟,這是一個由900多家成員公司組成的開放行業標準。

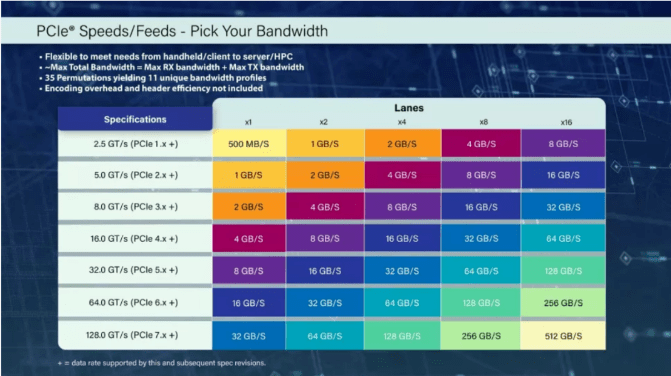

PCI-SIG指出,PCIe7.0接口將通過x16連接提供高達512GB/s的雙向吞吐量,但這是在編碼開銷(encodingoverhead)和標頭效率(headerefficiency)的影響之前,這兩者都會影響可用帶寬。

PCIe 7.0接口將繼續使用1b/1b flit模式編碼和PCIe 6.0引入的PAM4信號技術,這比3.0至5.0規格使用的128b/130b編碼和NRZ信號有明顯的改進。因此,實際可用帶寬將略低于 512 GB/s,但仍然代表著比PCIe 6.0接口翻了一番。

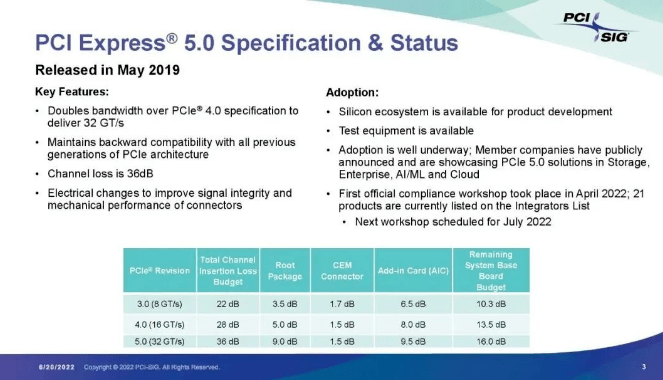

正如我們在跳轉到PCIe4.0和5.0時看到的那樣,由于更快的信號傳輸速率,PCIe走線的長度將再次縮短。這意味著在沒有額外組件的情況下,PCIe根設備(如CPU)和終端設備(如GPU)之間的最小允許距離將縮短。因此,與我們在前幾代接口中看到的相比,主板將需要更多的重定時器(retimers)和由更高質量材料組成的更厚PCB,而PCIe7.0支持將導致主板價格再次上漲。

值得注意的是,每條通道的帶寬將更高,現在對于x1連接的雙向帶寬為32GB/s,可以允許某些設備的“更細”連接(例如,使用x4而不是x8連接)。

PCIe7.0規范的基礎工作是在PCI-SIG今年早些時候完成PCIe6.0規范之后制定的,它將提供比上一代PCIe6.0接口增加一倍的帶寬。然而,我們還需要一段時間才能看到支持這種快速接口的SSD和GPU等設備——這些規范通常在我們看到出貨硅片之前很久就得到批準和最終確定。

您會注意到,市場上仍然沒有多少PCIe5.0設備,盡管該接口確實出現在英特爾AlderLake的主流主板上,并且還將出現在AMD即將推出的Zen4Ryzen7000上今年晚些時候到貨的平臺。首批PCIe5.0SSD將與Ryzen7000處理器同時上市,但我們已經看到了用于數據中心和AI/ML設備的PCIe5.0設備的產品公告。

換句話說,您在相當長的一段時間內都不會在市場上看到PCIe7.0設備,盡管PCI-SIG現在開始定義規范并希望實現其每三年發布一個新規范的目標。PCIe7.0規范預計將在2025年落地,但我們要到2028年才能看到終端設備。

PCIe7.0規范目標:

通過x16配置提供128GT/s的原始比特率和高達512GB/s的雙向傳輸速率

利用PAM4(4級脈沖幅度調制)信令

關注渠道參數和覆蓋范圍

繼續提供低延遲和高可靠性的目標

提高電源效率

保持與所有前幾代PCIe技術的向后兼容性

符號列表

“30年來,PCI-SIG的指導原則一直是,‘如果我們建造它,他們就會來,’”Insight64研究員NathanBrookwood說。“PCI技術的早期并行版本可容納數百兆字節/其次,與1990年代的圖形、存儲和網絡需求相匹配。2003年,PCI-SIG演變為支持千兆字節/秒速度的串行設計,以適應更快的固態磁盤和100MbE以太網。幾乎就像發條一樣,PCI-SIG每三年將PCIe規范帶寬翻一番,以應對新興應用和市場的挑戰。今天宣布的PCI-SIG計劃將通道速度翻倍至512GB/s(雙向)使其有望在另一個3年周期內將PCIe規范性能翻一番。”他進一步指出。

“隨著即將推出的PCIe7.0規范,PCI-SIG繼續我們30年來的承諾,即提供推動創新邊界的行業領先規范,”PCI-SIG總裁兼主席AlYanes說。“隨著PCIe技術不斷發展以滿足高帶寬需求,我們工作組的重點將放在通道參數和覆蓋范圍以及提高功率效率上。”AlYanes接著說。

PCIe7.0規范旨在支持新興應用,例如800G以太網、AI/ML、云和量子計算;和數據密集型市場,如超大規模數據中心、高性能計算(HPC)和軍事/航空航天。